HIGH VELOCITY N-ON AND N-OFF MODULATION DOPED GAAS/A1 Ga\_1-x As FETS

T. J. Drummond, S. L. Su, W. Kopp, R. Fischer, R. E. Thorne and H. Morkoç

Department of Electrical Engineering and Coordinated Science Laboratory University of Illinois 1101 W. Springfield, Urbana, Illinois 61801 Phone (217) 333-0722 and

K. Lee and M. S. Shur

Department of Electrical Engineering University of Minnesota Minneapolis, MN 55455

#### ABSTRACT

The purpose of this work is to determine the optimum design parameters of modulation doped Al<sub>x</sub>Ga<sub>l-x</sub>As/GaAs field effect transistors (MODFETs). An analytical model for MODFETs was developed and used to characterize several 1 µm gate transistors. Extremely high transconductances were obtained and are attributed to large electron saturation velocities in the undoped GaAs. At 300 K transconductances of 250 mS/mm and 235 mS/mm have been obtained for normally-off and normally-on devices respectively. At 77 K a transconductance of 400 mS/mm was obtained for a normally-off MODFET. Using our model to characterize these devices requires the electron saturation velocity to be about 2 x 10 cm/s at 300 K and 3 x 10 cm/s at 77 K.

#### INTRODUCTION

Modulation doped (Al,Ga)As/GaAs field effect transistors are being investigated for their high current per unit gate length and high transconductances. If MODFETs are to be employed in large scale integrated circuits to increase switching speed, devices should be designed to maximize the transconductance. For this purpose we have developed an analytical model to describe the transfer characteristics of MODFETs (1,2). Although MODFETs are fabricated like MESFETs, charge control by the gate is similar to that of a MOSFET due to the two dimensional nature of the charge carriers.

MODFETs are inherently superior to SiO2/Si MOSFETs for the following reasons. Both normallyon (N-on) and normally-off (N-off) devices can be fabricated on the same wafer without the need for an implantation or diffusion. Much larger mobilities and electron saturation velocities are obtainable in the undoped GaAs (3,4). The (A1,Ga)As/GaAs heterointerface where the conduction electrons are confined is virtually free of interface states and is smoother than the SiO2/Si interface. The enhanced low field mobilities of modulation doped structures have been found to have a relatively small effect in détermining device performance. The large transconductances observed are the result of the high electron saturation velocity in the GaAs. Using our model we estimate electron velocities of about 2 x 10' cm/s at 300 K and 3 x 10' cm/s at 77 K.

To take advantage of the high electron velocity and increased transconductance, theory indicates that the separation between the gate and and charge transfer across the heterojunction be maximized. In this report we demonstrate that this can be accomplished by decreasing the thickness of the undoped (Al,Ga)As spacer layer typically left at the heterointerface.

the two dimensional electron gas (2DEG) be minimized

#### EXPERIMENTAL

The Alo, 33 Gao. 67 As/GaAs heterostructures were grown by molecular beam epitaxy on (100) oriented Cr-doped GaAs substrates. The structure consisted of 1 µm of undoped GaAs, a layer of undoped Alo.33Gao.67As of thickness di, and 600 Å of  $\Lambda1_{0.33}$  Ga $_{0.67}$  As doped with Si to a level of 1 x  $10^{18}$ cm-3. Split source field effect transistors were then fabricated with AuGe/Ni/Au ohmic contacts for the source and drain. The gate metal was aluminum. The devices had a gate width of 290 µm and a gate length of 1 µm in a 3 µm channel. Both normallyoff and normally-on devices were fabricated from each wafer by controlling the depth to which the Al gate was recessed into the doped Alo.33Gao.67As. Details of the growth and fabrication have been reported elsewhere (5,6).

# THEORETICAL

When a doped (Al, Ga) As layer is grown on top of an undoped GaAs layer a 2DEG is formed at the interface due to the difference in the electron affinity of these layers. The amount of charge transfer across the interface is found by equating the charge depleted from the (Al, Ga) As to the charge accumulated in the potential well. A solution is then found such that the Fermi level is constant across the heterointerface. Such a solution has been found using the depletion approximation (7). We have found, however, that for typical doping densities this solution is not accurate enough. The reason for this is that the electrons in the (Al, Ga) As are nearly degenerate leading to a smaller space charge at the edge of the depletion layer. This results in a smaller interface electric field and interface electron density, nso, than predicted by the depletion approximation. We have obtained both numerical and approximate analytical solutions for n our analytical solution (8)

$$n_{so} = \sqrt{N_d^2 (d_i + \Delta d)^2 + (2\epsilon N_d/q) (\Delta E_c + \delta (\Delta E_c) - E_{F2}) - N_d (d_i + \Delta d)}$$

(1)

is obtained using a linearized dependence of the Fermi level on  $n_{SO}$  (see ref. 1 and 2). Here  $N_d$  is the donor density,  $d_i$  is the thickness of the undoped (Al,Ga)As layer,  $\Delta d = 80$  Å is a constant related to the EF vs.  $n_{SO}$  curve (1,2),  $\varepsilon$  is the dielectric permittivity of (Al,Ga)As, q is the electronic charge,  $\Delta E_c$  is the discontinuity in the conduction band,

$$\delta(\Delta E_c) = -(kT/q) [\ln(1+g'y) + (4/N_d') \ln(1+\chi y)]$$

(2)

and  $y = [((1 - \frac{1}{4}N_d^{\dagger})^2 + 4g^{\dagger}N_d^{\dagger})^{\frac{1}{2}} - (1 - \frac{1}{4}N_d^{\dagger})]/2g^{\dagger}$  (3)

where

$$N_d' = N_d/N_c$$

,  $g' = gexp(q\epsilon_d/kT)$  (4)

and

$$y = \exp(-qE_{F2}/kT).$$

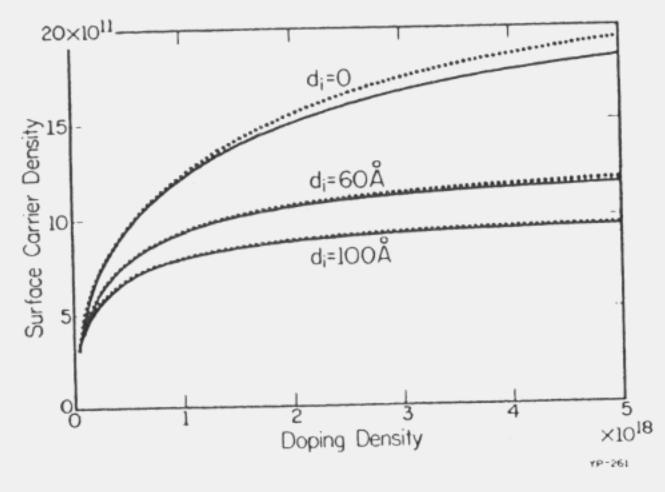

Here  $E_{F2}$  is the energy difference between the bottom of the conduction band and the Fermi level in the (A1,Ga)As,  $N_c$  is the density of states in (A1,Ga)As, g is the donor g-factor and  $\varepsilon_d$  is the donor ionization energy. Comparison of the exact solution (dotted line) with our analytical expression for  $n_{SO}$  (solid line) in Fig. 1 illustrates the accuracy of the approximation.

Fig. 1 Interface carrier density, n<sub>so</sub>, as a function of doping density, N<sub>d</sub>, with various undoped (Al,Ga)As layer thicknesses. The dotted line is the exact solution and the solid line is the analytical expression, eq. (1).

The expression for  $n_{SO}$  given in reference (7) is recovered if one assumes  $\delta \rightarrow 0$ . The actual value of  $\delta$  is close to -0.1 V. This may explain why the value of  $\Delta E_{C}/\Delta E_{g}=0.56$ , smaller than a generally accepted value of  $\Delta E_{C}/\Delta E_{g}=0.85$  (9) was used in reference (10) for the best fit with the experimental data. These results may be used in modelling MODFETs.

Placing a Schottky gate on the (Al,Ga)As results in a certain amount of depletion beneath the gate. If the (Al,Ga)As layer is thin enough or a sufficiently large negative gate voltage is applied, the gate and junction depletion regions will overlap. The density of the 2DEG is approximately described by the modified charge control model

$$n_s = (\varepsilon/q)[(V_g - V_{off})/(d + \Delta d)]$$

where d =  $d_d$  +  $d_i$ , where  $d_d$  is the thickness of doped (Al,Ga)As layer,  $V_{\rm off}$  =  $\phi_b$  -  $\Delta E_c$  -  $\Delta E_{\rm FO}$  where  $\phi_b$  is the Schottky barrier height,  $\Delta E_{\rm FO}$  temperature dependent parameter of our model and  $V_{\rm P2}$  =  $qN_{\rm d}d_0^2/2\varepsilon$ . Typically  $\Delta E_{\rm FO}$  is small the order of 20 mV).

The current-voltage characteristics were lated assuming that the current saturates when electric field at the drain side of the gate ceeds the velocity saturation field  $F_s = v_s/\mu$ longitudinal field distribution in the channe low the saturation voltage was described usin Shockley model (7,11). Analytical equations obtained describing the I-V characteristics ( cluding the effects of the source resistance) two piece linear (1) and three piece linear ( models for the velocity vs. electric field cu Both models take into account velocity satura in the channel. The latter model includes, i addition, the field dependence of the low fie mobility which is especially important at 77 have also calculated capacitance-voltage char istics (2).

Based on our model we have derived the foing expression for the maximum "intrinsic" tr conductance of the device, i.e. the transcond tance for  $R_{\rm S} = 0$ .

$$(g_{\rm m})_{\rm max} = (q\mu n_{\rm so}/L) [1 + (q\mu n_{\rm so}(d + \Delta d)/\epsilon v_{\rm s}L)^2]^{-\frac{1}{2}}$$

where  $g_m$  is the intrinsic transconductance pegate length,  $\mu$  is the low field mobility,  $\nu_{\text{S}}$  saturation velocity and

$$d = d_i + [2\epsilon(V_{Bi} - V_{off})/qN_d]^{\frac{1}{2}}$$

where  $V_{Bi} = \phi_b - \Delta E_c$  is the effective built-i tage. One of the consequences of eqs. (6) an is higher doping of the (Al,Ga)As reduces the mum thickness of the doped (Al,Ga)As beneath gate given by the second term in the right si eq. (7), leading to a higher transconductance

Our results indicate that at small gate 1 the transconductance becomes nearly independe the gate length due to velocity saturation. reality, an additional enhancement of the traductance in short gate structures is possible to ballistic effects. For very short gate le when

$$q\mu n_{so}(d + \Delta d)/\epsilon v_s L >> 1$$

we find  $(g_m)_{max}^{short} = \epsilon v_s/(d+\Delta d)$ . This expres together with eq. (7) sets an upper limit for transconductance of short gate MODFETs.

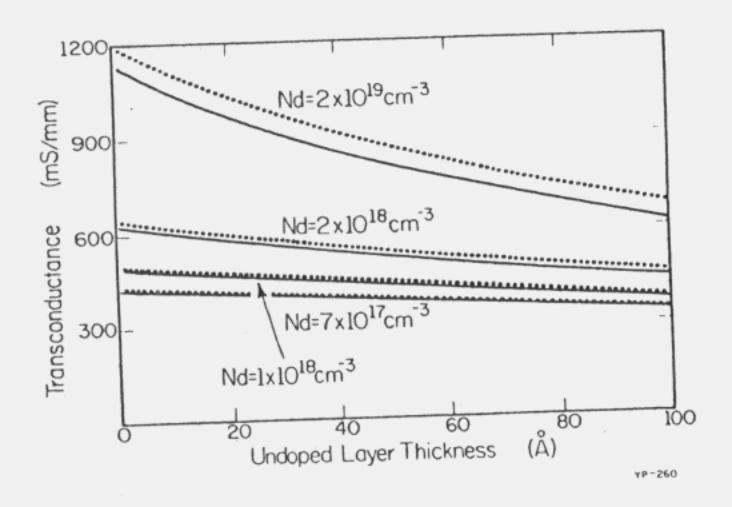

At room temperature when  $\mu$  is only a weak tion of  $d_i$ , the transconductance should increboth with a decrease in  $d_i$  (in agreement with imental results) and with a decrease in gate Assuming  $V_{Bi} = 0.7$  V,  $\Delta d = 80$  Å (7),  $\mu = 7000$  Vs, independent of  $d_i$  at 300 K (3), and  $v_s = 10^7$  cm/s we calculate  $(g_m)_{max}$  as a function of for a 1  $\mu m$  gate N-off device. The results ar shown in Fig. 2. The transconductance is consably larger for small values of  $d_i$ , especiall higher

\_\_\_

doping levels. This result is in agreement with our experimental data.

Fig. 2 Transconductance per mm gate as a function of the undoped layer thickness,  $V_{\rm off}$  = 0.2 V,  $\mu$  = 7000 cm<sup>2</sup>/Vs, L = 1  $\mu$ m. For the solid lines the degeneracy of the electrons in the (Al,Ga)As is taken into account and for the dotted lines it is neglected.

# RESULTS

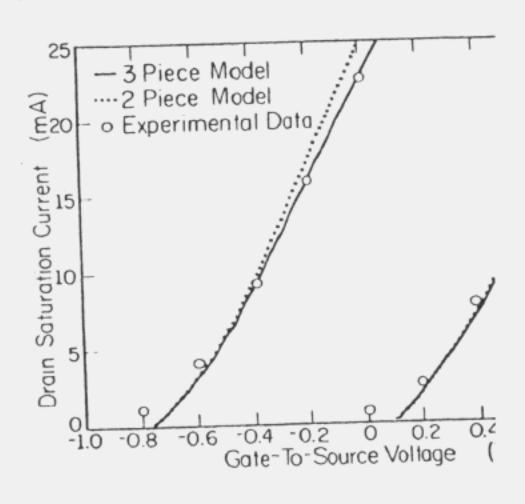

Field effect transistors were fabricated from heterostructures with the undoped (A1,Ga)As layer 100, 80, 60, 40 and 20 Å thick. Both current and transconductance increased by a factor of two as di was decreased from 100 to 20 Å. At 300 K the maximum values of transconductance were 250 mS/mm and 235 mS/mm for N-off and N-on devices respectively. The maximum currents were 131 mA/mm and 190 mA/mm respectively. The source resistance was 3.5 ohms for the N-on device and 5 ohms for the N-off device assuming an electron saturation velocity of 2 x 10' cm/s. The results of fitting the saturation current vs. gate voltage data with our model for a N-on and N-off MODFET are shown in Fig. 3. The data represent experimental points, the dotted and solid lines represent the fits using the two and three piece linear models respectively.

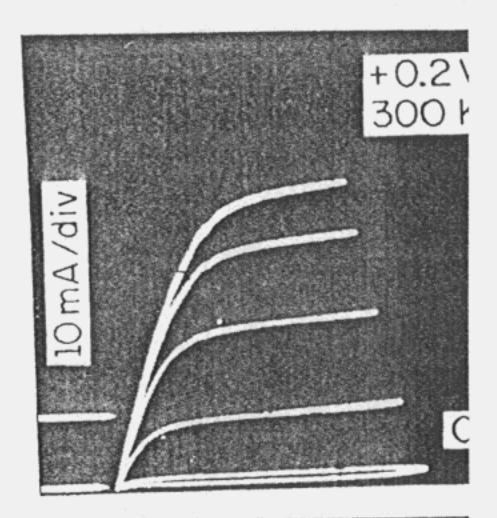

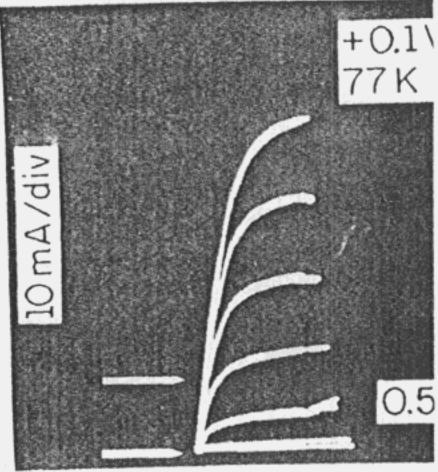

The drain I-V characteristics of a N-off device mounted on a TO-18 header at 300 K and 77 K are shown in Fig. 4. This device, with a 20 Å undoped layer, had a transconductance of 225 mS/mm and a current of 114 mA/mm at 300 K and a gate voltage of + 0.6 V. At 77 K the transconductance increased to 400 mS/mm and the current to 150 mA/mm at the same gate bias. The threshold voltage was observed to shift by about + 0.2 V at 77 K. Bulk (A1,Ga)As doped to 1 x  $10^{18}~\rm cm^{-3}$  with Si shows a 25% freezeout of electrons which is sufficient to account for the shift in the threshold voltage. To model the saturation current vs. gate voltage characteristic of this device at 300 K a source resistance of 4 ohms and a saturation electron velocity of 2 x  $10^7$  cm/s were used. At 77 K the source resistance was decreased to 2.5 ohms and the

electron velocity increased to 3 x 10

Fig. 3 Saturation current vs. gate verification for a N-on  $(d_i = 40)$   $(d_i = 20)$  Å) MODFET showing the fit to the experimental data.

Fig. 4 Drain I-V characteristics o  $(d_i = 20 \text{ Å})$  at 300 K (top)

fit the theoretical curve to the experimental data. These velocities are in extremely good agreement with predictions based on pulsed measurements (5).

As a final note, small signal microwave measurements were performed on a normally-off MODFET with a 60 Å undoped (Al,Ga)As layer. Although a maximum available gain as high as 10.8 dB was measured at 10 GHz the typical figure was 9 dB at 8 GHz.

#### CONCLUSIONS

The parameters optimizing the modulation doped field effect transistors (MODFETs) have been investigated. In accordance with the predictions of an analytical model developed for MODFETs, reducing the separation between the gate and the 2DEG increases the transconductance significantly. Device performance for short gate MODFETs is then limited by the electron saturation velocity rather than the mobility. Electrons at the heterointer- face exhibit saturation velocities of about 2 x 10 cm/s at 300 K and 3 x 10 cm/s at 77 K.

Fabricating a series of 1  $\mu m$  gate MODFETs with progressively thinner undoped (A1,Ga)As spacer layers resulted in higher transconductances and larger currents. Maximum transconductances at 300 K were 235 mS/mm and 250 mS/mm for N-on and N-off devices respectively. At 77 K a normally-off device had a transconductance of 400 mS/mm. By using a larger mole fraction and higher doping level our theory predicts that intrinsic transconductances of over 900 mS/mm may be possible.

# ACKNOWLEDGEMENTS

The work at the University of Illinois is funded by the Air Force Office of Scientific Research and the Joint Scrvices Electronics Program. The work at the University of Minnesota is partially funded by the Army Research Office and Honeywell, Inc. The authors would like to express their thanks to Drs. E. Hall and H. Goronkin and Mr. T. Miers of Motorola for providing the FET masks. The technical assistance of J. Klem, D. Arnold and W. G. Lyons is greatly appreciated.

# REFERENCES

- (1) T. J. Drummond, H. Morkoc, K. Lee and M. S. Shur, "Model for Modulation Doped Field Effect Transistor," IEEE Electron Dev. Lett., in print.

- (2) K. Lee, M. S. Shur, T. J. Drummond, H. Morkoç, "Current-Voltage and Capacitance-Voltage Characteristics of Modulation Doped Field Effect Transistors," unpublished.

- (3) T. J. Drummond, W. Kopp, M. Keever, H. Morkoç and A. Y. Cho, "Electron Mobilities in Single and Multiple Period Modulation Doped (Al,Ga)As/ GaAs Heterostructures," J. Appl. Phys., Vol. 53, pp. 1023-1027:1982.

- (4) T. J. Drummond, W. Kopp, H. Morkoç and M. Keever, "Transport in Modulation Doped Structures (Al<sub>x</sub>Ga<sub>1-x</sub>As/GaAs) and Correlations with Monte Carlo Calculations (GaAs)," Appl. Phys. Lett., Vol. 41, pp. 277-279:1982.

- (5) T. J. Drummond, H. Morkoç and A. Y. Cho, "MBE Growth of (A1,Ga)As/GaAs Heterostructures," J. Cryst. Growth, Vol. 56, pp. 449-454:1982.

- (6) S. L. Su, R. Fischer, T. J. Drummond, W. G. Lyons, R. E. Thorne, W. Kopp and H. Morkoç, "Modulation Doped (Al,Ga)As/GaAs FETs with High Transconductance and Saturation Velocity," Electron. Lett., in print.

- (7) D. Delagebeaudeuf and N. T. Linh, "Metal-(n)AlGaAs-GaAs Two-Dimensional Electron Gas FET," IEEE Elect. Dev., Vol. ED-29, pp. 955-960:1982.

- (8) K. Lee, M. S. Shur, T. J. Drummond and H. Morkoc, "Electron Density of the 2-d Electron Gas in Modulation Doped Layers," unpublished.

- (9) R. Dingle, "Confined Carrier Quantum States in Ultrathin Semiconductor Heterostructures," Festkorperprobleme XV, ed. H. Queisser, Pergamon-Vieweg, pp. 21-48:1975.

- (10) D. Delagebeaudeuf, P. Delescluse, P. Etienne, M. Laviron, J. Chaplart and N. T. Linh, "Two-Dimensional Electron Gas M.E.S.F.E.T. Structure," Electron. Lett., Vol. 16, pp. 667-668: 1982.

- (11) P. L. Hower and G. Bechtel, "Current Saturation and Small Signal Characteristics of GaAs Field Effect Transistors," IEEE Trans. Elect. Dev., Vol. ED-20, pp. 213-220:1973.