# Physical-gap-channel graphene field effect transistor with high on/off current ratio for digital logic applications

Jeong Hun Mun and Byung Jin Cho

Citation: Appl. Phys. Lett. 101, 143102 (2012); doi: 10.1063/1.4756795

View online: http://dx.doi.org/10.1063/1.4756795

View Table of Contents: http://apl.aip.org/resource/1/APPLAB/v101/i14

Published by the American Institute of Physics.

#### **Related Articles**

Light emission and current rectification in a molecular device: Experiment and theory J. Appl. Phys. 112, 113108 (2012)

Rectifying and perfect spin filtering behavior realized by tailoring graphene nanoribbons J. Appl. Phys. 112, 114319 (2012)

Spin filter and molecular switch based on bowtie-shaped graphene nanoflake J. Appl. Phys. 112, 104328 (2012)

Universal scaling of resistivity in bilayer graphene

Appl. Phys. Lett. 101, 223111 (2012)

Charge redistribution in a charge storage layer containing C60 molecules and organic polymers for long electron retention

APL: Org. Electron. Photonics 5, 252 (2012)

#### Additional information on Appl. Phys. Lett.

Journal Homepage: http://apl.aip.org/

Journal Information: http://apl.aip.org/about/about\_the\_journal Top downloads: http://apl.aip.org/features/most\_downloaded

Information for Authors: http://apl.aip.org/authors

### ADVERTISEMENT

## Physical-gap-channel graphene field effect transistor with high on/off current ratio for digital logic applications

Jeong Hun Mun and Byung Jin Cho<sup>a)</sup>

Department of Electrical Engineering, KAIST, 291 Daehak-ro, Yuseong-gu, Daejeon 305-701, South Korea

(Received 22 January 2012; accepted 17 September 2012; published online 1 October 2012)

We propose and analyze an approach to secure a high on/off current ratio in a graphene field effect transistor (FET) by introducing a physical gap along the channel rather than by attempting to open the energy bandgap of graphene. The device simulation results of the newly proposed device structure reveal highly suppressed off-state current of  $\sim 10^{-9} \, \text{A/}\mu\text{m}$ , an on/off current ratio of more than seven orders of magnitude, and a subthreshold slope of 2.23 mV/decade more than a 20-fold reduction relative to the theoretical limitation of conventional metal-oxide-semiconductor FETs. © 2012 American Institute of Physics. [http://dx.doi.org/10.1063/1.4756795]

Graphene field effect transistors (FETs) have been a subject of intense interest in recent years as researchers seek to replace current silicon based MOSFET technology. To date, most attempts to fabricate graphene FETs are based on a conventional metal-oxide-semiconductor FET (MOSFET) structure, with simple replacement of the channel material from silicon to graphene.<sup>1,2</sup> However, it must be noted that the current MOSFET structure has been designed and optimized for several decades for semiconducting materials, especially silicon, not for semimetal materials such as graphene. Therefore, simple replacement of the channel material in the conventional MOSFET structure necessitates efforts in opening the bandgap of graphene. Even though extensive efforts have been made to open up the energy bandgap of graphene, 3-11 it is found that the bandgap and carrier mobility are in a trade-off relationship in most materials. Once the energy bandgap is opened in graphene, its original physical properties are altered and degradation of carrier mobility is unavoidable. 1,12,13 It is also unrealistic to attain a bandgap of larger than 0.4 eV, which is the minimum practical requirement for digital circuit applications. Therefore, because graphene has a unique band structure that is substantially different from that of silicon, research on graphene transistors should take into consideration on device fundamentals, including device structure, rather than simply replacing the channel material and opening the bandgap.

In this perspective, various promising approaches, graphene nanoribbon tunnel graphene transistors, <sup>14,15</sup> bilayer pseudospin field effect transistors (BiSFET), <sup>16</sup> and Veselago lens switch, <sup>17,18</sup> exhibit promising results and strengthen the fundamentals of graphene FET. However, these devices require precise control of doping concentration or advanced fabrication technique for highly complex device, hindering the realization of graphene logic device.

In this work, we propose a device structure that does not require opening the bandgap of graphene and therefore can fully utilize the original unique properties of graphene. This device employs a physical-gap along the channel instead of opening graphene's energy bandgap, and is designed with consideration of producibility and compatibility to conventional complementary-MOS (CMOS) process technology.

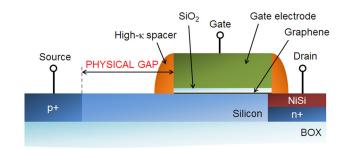

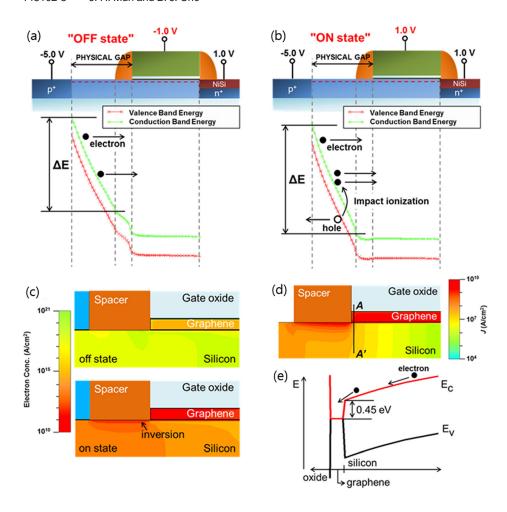

The physical-gap-channel graphene transistor is designed based on the impact-ionized MOS (IMOS) structure and implemented on a silicon-on-insulator (SOI) substrate (Fig. 1). The channel is composed of a series connection of an ungated silicon region (physical gap) and a graphene/silicon hybrid channel upon which the gate dielectric and electrode are formed. The silicon body is almost intrinsic (very lightly p-doped), and the source is  $p^+$  doped while the drain is  $n^+$  doped. High- $\kappa$  dielectric spacer is placed at the side of the gate stack. Nickel silicide is formed in the drain region for good ohmic contact, as is quite commonly employed in advanced CMOS devices.

The physical-gap-channel graphene transistor is designed on a SOI substrate that has a 20 nm thick silicon body. The lengths of the graphene/silicon hybrid channel and the physical gap are 100 and 80 nm, respectively. The physical thickness of the gate dielectric is 2 nm and the width of the high- $\kappa$  spacer is 20 nm. Here, the dielectric constant of the high- $\kappa$  spacer is assumed to be 40, which can be realized by using cubic structured La-doped HfO<sub>2</sub>. N<sup>+</sup> polysilicon is used for the gate electrode. The silicon body is very lightly doped with p-type dopant with a concentration of  $1 \times 10^{15}$  cm<sup>-3</sup>. The source and drain are doped with p-type and n-type, respectively, with a doping concentration of  $1 \times 10^{20}$  cm<sup>-3</sup>. The operation behavior and feasibility of

FIG. 1. Illustration of the physical-gap-channel graphene transistor. The graphene channel under the gate is physically separated from the source edge. The source is  $p^+$  doped, while the drain is  $n^+$  doped. The silicon body is almost intrinsic. A high- $\kappa$  spacer is used to induce a fringing electric field to the silicon surface.

a) Author to whom correspondence should be addressed. Electronic mail: bjcho@ee.kaist.ac.kr.

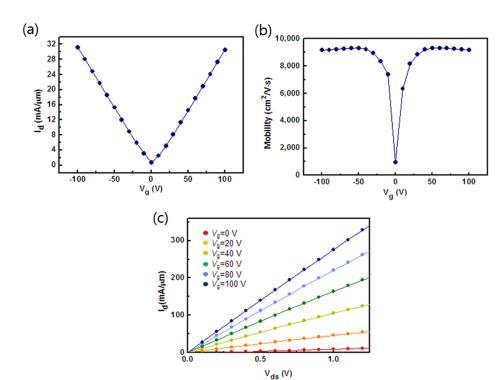

the devices are analyzed using commercial device simulation software, Technology Computer-Aided Design (TCAD), Silvaco. 19,22 Prior to the analysis of the proposed structure, the characteristics of a graphene back gate FET structure are analyzed to verify the suitability of the simulation tool for modeling the graphene transistor, because there is no physical model of graphene for a computer simulation in the commercial device simulator. In our simulation, the graphene is defined as a zero bandgap general semiconductor with a physical thickness of 1 nm, a work function of 4.5 eV, intrinsic carrier density of  $2 \times 10^{11}$  /cm<sup>2</sup>, and both hole and electron mobilities of  $10\,000\,\mathrm{cm^2/V \cdot s.^{23-26}}$  The simulation results of the back gate graphene FET with a 100 nm thick gate dielectric reveal typical characteristics of a graphene FET, including ambipolar conduction (Fig. 2(a)), zero bandgap, high mobility (Fig. 2(b)), and linear output characteristics (Fig. 2(c)), thus indicating that we can use this model for simulation of the physical-gap-channel graphene transistor. 23-28

The basic operation principle of the proposed graphene transistor is depicted in Fig. 3. When a negative bias is applied to the gate, the graphene under the gate becomes p-type. However, because of the presence of the physical gap along the channel, the device remains in an off-state and the drain current is limited by the reverse saturation current of the p-i-n junction. When the gate voltage is positive, the graphene becomes n-type. As the gate voltage is increased further, an electron inversion layer is formed underneath the high- $\kappa$  spacer by a fringing field. The surface regions from the drain to the edge of the high- $\kappa$  spacer in the physical gap region are then electrically connected. The formation of the electron inversion layer under the high- $\kappa$  spacer results in reduction of the effective length of the physical gap, causing an increase of the lateral electric field in this region (Fig. 3(b)). With higher gate voltage, the resistance between the drain and the edge of the high- $\kappa$  spacer in the physical gap region drops further, and then the lateral electric field in the physical gap is further enhanced at a given drain bias. This process eventually ignites the impact ionization in the physical gap region and electrons are injected from the valence band of the p<sup>+</sup> source into the physical gap region and thereby the device is turned on. It is known that the work function of graphene is around 4.5 eV. Then, the Fermi level of graphene is located within the bandgap of silicon as shown in Fig. 3(e). At the edge of the graphene channel region (near high-K spacer), the electrons in the silicon inversion region under high-K spacer region will flow to graphene due to the band offset between silicon conduction band and graphene, making it possible to fully exploit the high electron mobility of the graphene layer. As the switching of this device is controlled by the fringing field at the edge of the physical gap, the switching operation of this graphene FET is insensitive to the Dirac voltage and the initial doping concentration of graphene, which are almost uncontrollable quantities in conventional graphene FETs. <sup>29–31</sup> The engineered nickel silicide, which has a work function of 4.5 eV, helps provide barrier-less conduction of electrons from graphene to the drain electrode. The engineered nickel silicide, which has a work function of 4.5 eV, helps provide barrier-less conduction of electrons from graphene to the drain electrode. The drain biases used in this simulation are rather large, because the device requires avalanche breakdown in the physical gap region. However, several solutions are already suggested to address this issue, such as channel length scaling,<sup>32</sup> utilizing new material with high impact ionization coefficient, <sup>33</sup> introducing strain, <sup>34</sup> and so on.

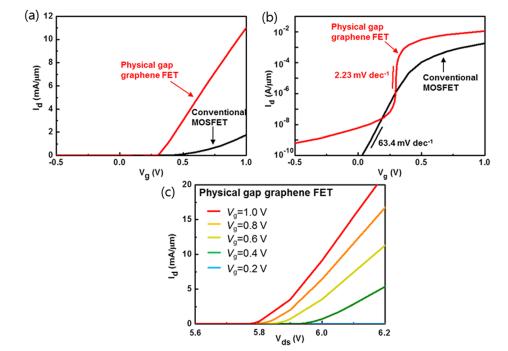

The calculated I-V characteristics of the proposed device are shown in Fig. 4. The physical dimension of the gated graphene channel length is fixed at 100 nm. A conventional n-channel silicon MOS device with the same gate channel length and a similar threshold voltage is simulated together for comparison. The graphene channel device shows

FIG. 2. The simulation result of the back gate graphene FET with a 100 nm thick gate dielectric. The graphene is defined as a zero bandgap general semiconductor with a physical thickness of 1 nm. (a)  $I_d$ - $V_g$  characteristics show ambipolar transport and a low on/off ratio. (b) Carrier mobility calculated from the  $I_d$ - $V_g$  curve by Drude model. (c)  $I_d$ - $V_d$  characteristics of the graphene transistor

FIG. 3. Operating bias conditions of the proposed device and corresponding energy band diagrams along the channel. (a) Band diagram in off state.  $V_{ds} = 6.0 \, V$  and  $V_{\alpha} = -1 \text{ V}$ . The energy band of silicon underneath the high- $\kappa$  spacer region is pulled up by negative gate bias. (b) In the on state, the energy band of silicon underneath the spacer region is pushed down, resulting in an increase of the lateral electric field in the physical gap region. This causes ignition of impact ionization, causing the device to turn on. (c) Current density distribution in channel area. In the on state  $(V_g = 1.0 \text{ V}, \ V_d = 1.0 \text{ V}, \ \text{and} \ V_s = -5.0 \text{ V}),$ almost all electrons flow through the graphene rather than through the silicon.

ten times higher on-state current compared to the conventional MOS device (Figs. 4(a) and 4(b)). More importantly, the proposed graphene device shows excellent switching performance with an on/off current ratio of seven orders of magnitude, which is well within the acceptable range for modern digital logic circuits (Fig. 4(b)). In addition, the graphene de-

vice exhibits a subthreshold slope of  $2.23\,\mathrm{mV/dec}$ , constituting more than a 20-fold reduction from the theoretical limitation of conventional MOS devices ( $\sim\!60\,\mathrm{mV/dec}$ ). This sudden switching behavior originates from the feature that the conduction is ignited by impact ionization in the physical gap region. However, the  $V_d$ - $I_d$  characteristic (Fig. 4(c))

FIG. 4. Transfer characteristics and device performance. (a) Linear-linear plot of  $I_d\text{-}V_g$  curve. (b) Log-linear plot of  $I_d\text{-}V_g$  curve. The physical-gap-channel graphene FET shows significantly suppressed off-state current and an ultra-steep subthreshold slope of 2.23 mV/dec. The characteristics of a conventional MOSFET that has the same channel length are plotted together for comparison. (c) The  $I_d\text{-}V_d$  characteristics of the graphene FET show a narrow operation window and small output resistance.

shows that the physical-gap-channel graphene device has low output resistance and a narrow operation voltage window, thus necessitating further optimization of the device structure in future research. And, it should be noted that the model which we used in this simulation does not include the physical limitation of current capacity of graphene and heating effect. Therefore, the current levels at further higher drain biases may be lower in actual devices.

In conclusion, significant suppression of the off-state current in the physical-gap-channel graphene transistor enables an on/off current ratio of seven orders of magnitude, the highest value that has been achieved to date in a graphene channel transistor. Excellent device performance including an extremely steep subthreshold slope and high on-state current is obtained through the innovative device structure. The proposed device utilizes the conventional CMOS process technology and therefore application of graphene channel FETs to digital logic devices is expected to become more realistic in the near future.

This work was supported by the National Research Foundation of Korea (NRF) Research Grant Nos. 2008-2002744, 2010-0029132, and 2011-0031638.

- <sup>1</sup>F. Schwierz, Nat. Nanotechnol. 5, 487 (2010).

- <sup>2</sup>A. K. Geim, Science **324**, 1530 (2009).

- <sup>3</sup>C. Berger, Z. Song, X. Li, X. Wu, N. Brown, C. Naud, D. Mayou, T. Li, J. Hass, A. N. Marchenkov, E. H. Conrad, P. N. First, and W. A. de Heer, Science 312, 1191 (2006).

- <sup>4</sup>M. Y. Han, B. Ozyilmaz, Y. Zhang, and P. Kim, Phys. Rev. Lett. 98, 206805 (2007).

- <sup>5</sup>E. McCann, Phys. Rev. B **74**, 161403 (2006).

- <sup>6</sup>Y. Zhang, T. T. Tang, C. Girit, Z. Hao, M. C. Martin, A. Zettl, M. F. Crommie, Y. R. Shen, and F. Wang, Nature 459, 820 (2009).

- <sup>7</sup>Z. H. Ni, T. Yu, Y. H. Lu, Y. Y. Wang, Y. P. Feng, and Z. X. Shen, ACS Nano 2, 2301 (2008).

- <sup>8</sup>S. M. Choi, S. H. Jhi, and Y. W. Son, Nano Lett. **10**, 3486 (2011).

- <sup>9</sup>J. O. Sofo, A. S. Chaudhari, and G. D. Barber, Phys. Rev. B 75, 153401

- <sup>10</sup>D. C. Elias, R. R. Nair, T. M. G. Mohiuddin, S. V. Morozov, P. Blake, M. P. Halsall, A. C. Ferrari, D. W. Boukhvalov, M. I. Katsnelson, A. K. Geim, and K. S. Novoselov, Science 323, 610 (2009).

- <sup>11</sup>L. Ci, L. Song, C. Jin, D. Jariwala, D. Wu, Y. Li, A. Srivastava, Z. F. Wang, K. Storr, L. Balicas, F. Liu, and P. M. Ajayan, Nature Mater. 9, 430

- <sup>12</sup>B. Obradovic, R. Kotlyar, F. Heinz, P. Matagne, T. Rakshit, M. D. Giles, M. A. Stettler, and D. E. Nikonov, Appl. Phys. Lett. 88, 142102 (2006).

- <sup>13</sup>A. Betti, G. Fiori, and G. Iannaccone, Appl. Phys. Lett. **98**, 212111 (2011). <sup>14</sup>Q. Zhang, T. Fang, H. Xing, A. Seabaugh, and D. Jena, IEEE Electron Device Lett. 29, 1344 (2008).

- <sup>15</sup>G. Fiori and G. Iannaccone, IEEE Electron Device Lett. **30**, 1096 (2009).

- <sup>16</sup>S. K. Banerjee, L. F. Register, E. Tutuc, D. Reddy, and A. H. MacDonald, IEEE Electron Device Lett. 30, 158 (2009).

- <sup>17</sup>V. V. Cheianov, V. Fal'ko, and B. L. Altshuler, Science 315, 1252 (2007).

- <sup>18</sup>J. R. Williams, T. Low, M. S. Lundstrom, and C. M. Marcus, Nat. Nanotechnol. 6, 222 (2011).

- <sup>19</sup>F. Mayer, C. Le Royer, G. Le Carval, L. Clavelier, and S. Deleonibus, IEEE Trans. Electon Devices 53, 1852 (2006).

- <sup>20</sup>W. He, L. Zhang, D. S. H. Chan, and B. J. Cho, IEEE Electron Device Lett. 30, 623 (2009).

- <sup>21</sup>J. K. Park, Y. Park, M. H. Song, S. K. Lim, J. S. Oh, M. S. Joo, K. Hong, and B. J. Cho, Appl. Phys. Express 3, 091501 (2010).

- <sup>22</sup>J. A. Salcedo, J. J. Liou, L. Zhiwei, and J. E. Vinson, IEEE Trans. Electron Devices 54, 822 (2007).

- <sup>23</sup>A. K. Geim and K. S. Novoselov, Nature Mater. **6**, 183 (2007).

- <sup>24</sup>Y. W. Tan, Y. Zhang, K. Bolotin, Y. Zhao, S. Adam, E. H. Hwang, S. Das Sarma, H. L. Stormer, and P. Kim, Phys. Rev. Lett. 99, 246803 (2007).

- <sup>25</sup>J. Nilsson, A. H. Castro Neto, F. Guinea, and N. M. R. Peres, Phys. Rev. Lett. 97, 266801 (2006).

- <sup>26</sup>M. I. Katsnelson, Eur. Phys. J. B **51**, 157 (2006).

- <sup>27</sup>K. Nomura, and A. H. MacDonald, Phys. Rev. Lett. **98**, 076602 (2007).

- <sup>28</sup>Y. M. Lin, K. A. Jenkins, A. Valdes-Garcia, J. P. Small, D. B. Farmer, and P. Avouris, Nano Lett. 9, 422 (2009).

- <sup>29</sup>C. Casiraghi, S. Pisana, K. S. Novoselov, A. K. Geim, and A. C. Ferrari, Appl. Phys. Lett. 91, 233108 (2007).

- <sup>30</sup>K. F. Mak, M. Y. Sfeir, Y. Wu, C. H. Lui, J. A. Misewich, and T. F. Heinz, Phys. Rev. Lett. 101, 196405 (2008).

- <sup>31</sup>Y. Shi, X. Dong, P. Chen, J. Wang, and L. J. Li, Phys. Rev. B **79**, 115402 (2009)

- <sup>32</sup>W. Y. Choi, J. Y. Song, J. D. Lee, Y. J. Park, and B. G. Park, Tech. Dig. -Int. Electron Devices Meet. 2005, 955-958.

- <sup>33</sup>K. Gopalakrishnan, P. B. Griffin, and J. D. Plummer, IEEE Electron Device Lett. 52, 69 (2005).

- <sup>34</sup>G. H. Wang, L. Chan, G. Q. Lo, G. Samudra, and Y. C. Weo, IEEE Trans.

- Electron Devices 54, 2778 (2007).