-0.085 10 0

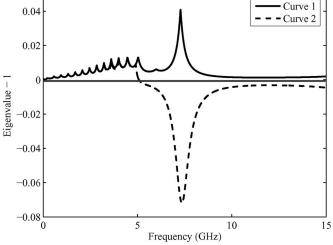

Fig. 3. Eigenvalue plot of real part of admittance matrix.

#### VI. CONCLUSION

In this paper, a novel formulation of TE is presented, which enables the inclusion of PR matrix rational approximation of FD-PUL parameters directly in the TEs and does not require the explicit lumped-circuit realization in terms of positive elements. The resulting reduced model of the TEs using the ICT technique is guaranteed to be passive.

#### REFERENCES

- [1] R. Achar and M. Nakhla, "Simulation of high-speed interconnects," Proc. IEEE, vol. 89, no. 5, pp. 693-728, May 2001.

- [2] Q. Yu, J. M. L. Wang, and E. S. Kuh, "Passive multipoint moment matching model order reduction algorithm on multiport distributed interconnect networks," IEEE Trans. Circuits Syst. I, Fundam. Theory Appl., vol. 46, no. 1, pp. 140-160, Jan. 1999.

- [3] E. Gad and M. Nakhla, "Efficient simulation of nonuniform transmission lines using integrated congruence transform," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 12, no. 12, pp. 1307-1320, Dec. 2004.

- [4] C. Chen, E. Gad, M. Nakhla, and R. Achar, "Analysis of frequencydependent interconnects using integrated congruence transform," IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., vol. 26, no. 6, pp. 1139-1149, Jun. 2007.

- [5] C. Paul, Analysis of Multiconductor Transmission Lines. New York: Wiley, 1994.

- [6] T. Palenius and J. Roos, "Comparison of reduced-order interconnect macromodels for time-domain simulation," IEEE Trans. Microw. Theory Tech., vol. 52, no. 9, pp. 2240-2250, Sep. 2004.

- [7] D. Saraswat, R. Achar, and M. Nakhla, "Global passivity enforcement algorithm for macromodels of interconnect subnetworks characterized by tabulated data," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 13, no. 7, pp. 819-832, Jul. 2005.

- [8] B. Gustavsen and A. Semlyen, "Rational approximation of frequency domain responses by vector fitting," IEEE Trans. Power Del., vol. 14, no. 3, pp. 1052-1061, Jul. 1999.

- [9] S. Boyd, L. El Ghaoui, E. Feron, and V. Balakrishnan, Linear Matrix Inequalities in System and Control Theory, vol. 15. Philadelphia, PA: SIAM, 1994.

- [10] W. Arnold and A. Laub, "Generalized eigenproblem algorithms and software for algebraic Riccati equations," Proc. IEEE, vol. 72, no. 12, pp. 1746-1754, Dec. 1984.

# A Delay Line Circuit Design for Crosstalk Minimization **Using Genetic Algorithm**

Chaeho Chung, Soobum Lee, Byung Man Kwak, Gawon Kim, and Joungho Kim

Abstract-Most signals between chips or packages in an electric circuit board require certain delays in order to achieve good timing. An extension of the circuit line that is proportional to the designated time delay has been a usual practice due to cost effectiveness. However, the layout of the line becomes dense due to the small size of packages or circuit boards, and this generates crosstalk, causing signal detection errors. In this paper, a design methodology of delay line layout for crosstalk minimization is developed using the genetic algorithm (GA). The GA requires a large number of function evaluations, and efficient calculation of crosstalk is proposed together with a new technique of generating random line, making offsprings, and mutation. Different optimum results have been obtained for different objectives and compared. Some of the designs were actually manufactured and experimentally tested, showing the validity of the optimum results.

Index Terms-Crosstalk minimization, genetic algorithm (GA), optimum delay line layout.

### I. INTRODUCTION

With the competition for cheaper and smaller products, the need for low-cost and high-density circuit board increases. One of the important tasks encountered in the development of such a circuit board is to design delay line paths according to a designated signal delay. A widely accepted practice is to extend the circuit line in proportion to the desired time delay. However, the layout tends to become dense and twisted due to size limitation. These lines can cause a crosstalk which deteriorates the signal quality such as voltage drop, or jitter should be minimized.

For analyses of crosstalk, Wu and Chao [1] suggested a wavetracing technique and a quantitative analysis with the help of connection matrix. A laddering crosstalk analysis [2] and a method of moments are also proposed [3]. With the help of these or other analysis techniques, much endeavor to reduce crosstalk has been performed, for example, for wires in a VLSI chip [4]-[6], or by adjusting the line spacing [7]. A framework for fast multilevel routing, considering crosstalk and timing, has been proposed [8], and a similar routing problem has been solved using the genetic algorithm (GA) to minimize the crosstalk [9]; both of them optimize a chip-level routing. However, little study on layout changes in a PCB board has been reported even though much larger effect is expected.

Currently, the meander (or serpentine) line shape is mainly used in the industry due to its simple shape. However, the detail dimensions, such as the gaps between any two line and the line lengths, still need to be modified by trial and error [1], [2], [10], [11] in order to

Manuscript received February 24, 2007; revised July 20, 2007. This work was supported in part by Samsung endowment fund for Samsung Chair Professorship and in part by the IT R&D program of MIC/IITA (2005-S118-02, Development of High-Performance and Smallest SiP Technology). This paper was recommended by Associate Editor N. Chang.

C. Chung is with the Corporate R&D Center, LG Chem., Daejeon 305-380, Korea.

S. Lee and B. M. Kwak are with the Department of Mechanical Engineering, Korea Advanced Institute of Science and Technology, Daejeon 305-701, Korea (e-mail: sblee@khp.kaist.ac.kr).

G. Kim and J. Kim are with the Department of Electrical Engineering, Korea

Advanced Institute of Science and Technology, Daejeon 305-701, Korea. Digital Object Identifier 10.1109/TCAD.2008.915540

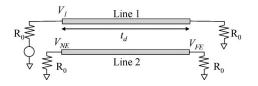

Fig. 1. Parallel transmission lines with matched transmission [11]. A pulse transmitted on the upper line generates crosstalk on the lower line.

reduce the high peak value of the crosstalk, which is known as the disadvantage of the meander line. The spiral line layout is suggested for this reason, whereas it produces a widely and asynchronously accumulated crosstalk [1], [10]. Although the concentric Cs delay has been proposed so as to keep the crosstalk closer to the input signal [11], it did not reduce the crosstalk compared with the spiral line. Existing delay lines show different shortcomings. Therefore, a systematic procedure is required to select among existing delay lines or to design a delay line following specific design requirements.

With this motivation, a procedure of simulation is first developed, and a general delay line design method is proposed in this paper.

### II. CROSSTALK CALCULATION

A single delay line case, rather than differential signaling, is mainly considered in this paper. Let us explain the crosstalk calculation by taking two adjacent parallel sections, as shown in Fig. 1. We assume that the crosstalk is generated only in the adjacent parallel line. The crosstalk decreases exponentially with the distance, and the effect from the next adjacent parallel lines is negligible.

If a ramped step pulse (the amplitude is  $V_{in}$ , and the rising time is  $T_r$ ) is introduced from the starting point at  $t_0$  and travels along the active line (line 1 or the aggressor), the capacitive and inductive couplings occur between two lines, and they cause the near-end (NE) and far-end (FE) crosstalk on the adjacent parallel line (line 2 or the victim) [12], [13]. The NE and FE crosstalk are proportional to  $V_{in}$ , and the proportional constants for each crosstalk are expressed as follows [14]:

$$k_{\text{NEXT}} = \frac{1}{4} \left( \frac{C_m}{C_{11}} + \frac{L_m}{L_{11}} \right)$$

$$k_{\text{FEXT}} = \frac{1}{2} \left( \frac{C_m}{C_{11}} - \frac{L_m}{L_{11}} \right)$$

(1)

where  $C_m$  and  $C_{11}$  are the mutual capacitance and the selfcapacitance, respectively, and  $L_m$  and  $L_{11}$  are the mutual inductance and the self-inductance, respectively. These capacitance and inductance are the functions of the distance between line 1 and line 2  $(s_l)$ [15], and other parameters (the width of the delay line, the height of PCB board, impedance, and so on) are assumed to be fixed. The NE crosstalk has positive voltage and moves leftward, whereas the FE crosstalk has negative voltage and moves rightward in line 2.

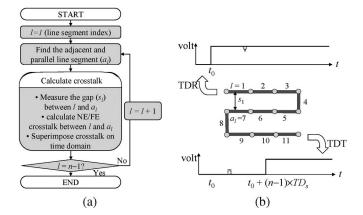

We predict the total crosstalk in a delay line by the superposition [15] upon the time domain from each line segment. The time delay of each segment is denoted as TD<sub>s</sub>. This numerical superposition procedure is summarized in Fig. 2 with a simple example. For the segmented line layout in Fig. 2 (the number of line segments is n - 1, and n = 12 in this example), we visit each line segment (l) in order and find a victim segment ( $a_l$ ). After measuring the gap ( $s_l$ ) between l and  $a_l$ , the NE/FE crosstalk, proportional to  $k_{\text{NEXT}}$  and  $k_{\text{FEXT}}$ , respectively, is calculated and superposed on the original time-domain reflectometry (TDR) and time-domain transmit (TDT) waveforms, as shown in Fig. 2. In this figure, the original waveform ( $W_i$ ) and the crosstalk ( $W_c$ ) are indicated by solid and dotted lines, respectively. For NE crosstalk in  $a_l$ , a 2 × TD<sub>s</sub> wide,  $k_{\text{NEXT}} \times V_{\text{in}}$  high, and rec-

Fig. 2. Procedure of crosstalk calculation. (a) Flow chart. (b) Case study.

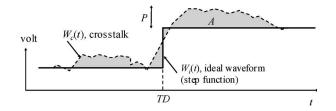

Fig. 3. Characteristics of crosstalk in TDT waveform.

tangular wave is superposed. For FE crosstalk in  $a_l$ , on the other hand, a  $T_r$  wide,  $k_{\text{FEXT}} \times V_{\text{in}}$  deep, and triangular wave is superposed. In either case, the crosstalk is superposed at  $t_0 + (l + a_l - 1) \times \text{TD}_s$  if it is toward TDR, or at  $t_0 + (n + l - a_l - 1) \times \text{TD}_s$  if it is toward TDT.  $a_l$  can be plural if there is any  $a_6 = 2$  and 10, for example. The procedure is repeated until l reaches n - 1.

# III. OPTIMIZATION STRATEGY USING GA

In this section, we present the design method of delay line circuits to minimize crosstalk using GA. The general GA is tailored for the line layout design; the ways of creating the initial pool, making offspring, and mutation are suggested.

### A. Optimization Formulation

In order to minimize the detection error caused by the distorted waveform with the crosstalk, harmful features of the crosstalk are chosen as objective functions to be minimized: the peak value (P), the total area of the unadulterated waveform (A), or the variance (V), as shown in Fig. 3 and in the following equations:

$$P = \max_{t} \{W_{c} - W_{i}\}$$

$$2TD_{i}$$

$$A = \int_{0}^{0} |W_{c} - W_{i}| dt$$

$$M = \int_{0}^{2} TD_{i} \frac{t|W_{c} - W_{i}|}{A} dt$$

$$V = \int_{0}^{2} TD_{i} \frac{(M - t)^{2}|W_{c} - W_{i}|}{A} dt$$

(2)

where  $\text{TD}_l(=(n-1) \times \text{TD}_s)$  is the time delay from the starting to the ending points.

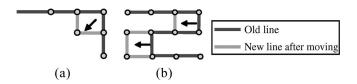

Fig. 4. Two ways of line modification without length change. (a) Point moving. (b) Conjugate moving.

A board that is defined as a rectangle is meshed, and a line is drawn by filling cells from the fixed starting point to the ending point. The design variable set  $\mathbf{X}$  consists of the x and y coordinates of the cells in the filling order, and its component is a natural number. The optimization formulation is expressed as follows:

Minimize

$$f = P(\mathbf{X}), A(\mathbf{X}), \text{ or } V(\mathbf{X})$$

(3)

$$|x_j - x_{j+1}| + |y_j - y_{j+1}| = 1,$$

$$j = 1, \dots, n-1$$

(5)

(4)

$$|x_i - x_j| + |y_i - y_j| > 0, \ i = 1, \dots, n,$$

$$j = 1, \dots, i - 1, i + 1, \dots, n$$

$$1 \le x_j \le C_{\text{width}}, 1 \le y_j \le C_{\text{width}},$$

(6)

$$j = 1, \dots, n, (x_j, y_j) \notin \mathbf{R}$$

(7)

where

$$\mathbf{X} = \begin{bmatrix} x_1 & x_2 & \dots & x_n \\ y_1 & y_2 & \dots & y_n \end{bmatrix}.$$

(8)

$(x_1, y_1)$  and  $(x_n, y_n)$  are given when the starting and the ending points are fixed.

The objective function is defined to be one of the features in the crosstalk, as shown in (3).  $C_{\rm width}$  and  $C_{\rm height}$  are the total number of the columns and the rows in the meshed rectangle. **R** is the set of points within an obstacle area where no line should pass. The constraints denote the following conditions: (5) line connectivity condition (any two consecutive locations should have a distance of 1), (6) the condition to prevent line overlapping, and (7) the upper limits and obstacles in the circuit where the line should not pass.

## B. Modified GA for Line Layout Design

An optimization method for line layouts is proposed using GA. First, we generate a number of lines to make the first pool (Section III-B1). Second, parent lines from the generated pool are selected. The third step is to make offspring to substitute worse lines in the pool. Finally, a new mutation scheme is performed, as explained in Section III-B3. These steps are repeated until the number of iteration reaches a predefined maximum iteration number [16].

1) Random Line Generation: For using GA, random chromosomes must be generated considering the constraints in (4)–(7). Each cell of a chromosome is represented by 3 bits: 1 bit for existence(1)/nonexistence(0) of line and 2 bits for the line extending direction [rightward(00), leftward(01), upward(10), and downward(11)]. The set of chromosomes uniquely defines **X**. The proposed random line generation technique is composed of the following three steps: path finding from the starting point to the ending point, line length matching, and line moving. The shortest and nonintersecting connected line is first found from the starting point to the ending point, not overlapping the obstacle. Next, the line length is randomly extended until it reaches the designated length (n - 1). Finally, the line layout is modified while keeping the line length and the constraints in (4)–(7) using two ways shown in Fig. 4: a "point moving" [Fig. 4(a)] or a

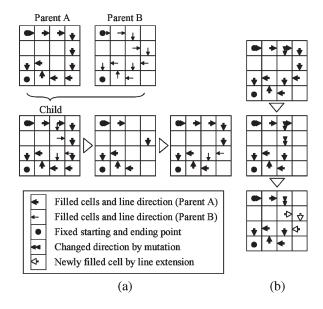

Fig. 5. Operations in the modified GA. (a) Making offspring. (b) Mutation.

TABLE I

Experiment Conditions for Crosstalk Measurement

| Item                                 | Quantity               |

|--------------------------------------|------------------------|

| Input voltage (V <sub>in</sub> )     | 250 mV                 |

| Impedance                            | 50 Ω                   |

| Rising time of step function $(T_r)$ | $70 \times 10^{-12} s$ |

"conjugated moving" [Fig. 4(b)]. We visit every single cell where a corner is made, and we change the shape if the objective function is improved by "point moving," as shown in Fig. 4(a). "Conjugate moving" in Fig. 4(b) is tried afterward for all possible pairs. A pool (the first generation) is created by performing these three steps repeatedly z times (the size of the population).

2) Selecting Parents and Making Offspring: We select parents from the pool made in the previous section. The lower the objective function value, the higher probability to be chosen as a parent is assigned. The probability for each line  $(p_G)$  varies from 0.05 (for the worst) to 0.55 (for the best). A random number in (0,1) is generated for each line in the pool, and the line is chosen as a member of the parent pool if the random number is less than  $p_G$ .

The line layouts of worse objective functions in a generation are erased. The probability to be erased  $(p_{\rm B})$  varies from 0.5005 (for the worst) to 0.0005 (for the best). A random number in (0,1) is again generated for each line, and the line is erased once it is less than  $p_{\rm B}$ .

The newly born offsprings by the crossover substitute the erased ones to maintain the total number of lines in a generation. The crossover operation for delay lines is suggested, as shown in Fig. 5(a). The chosen two parents A and B are overlapped [the first step at "Child" procedure in Fig. 5(a)], and the overlapped cells of the same direction remain (the second). Next, following the path from the starting point along the remaining line, when we meet a cut, we select the direction of Parent A or Parent B randomly until we reach the ending point. Finally, we adjust the line length using the method in Section III-B1 if the length is changed.

3) Mutation: A geometric mutation method for the line layout, as described in Fig. 5(b), is considered as follows: We generate a random real number in (0, 1) at every cell along the line from the starting point and perform mutation if the number is under a mutation probability  $p_M$  (0.005 is chosen). When a mutation is determined, the

Fig. 7. Waveform of meander delay line ( $V_t$  is minimized).

Fig. 8. Waveform of Dz delay line ( $A_t$  and  $A_r$  are minimized).

TABLE II

CHARACTERISTICS OF CROSSTALK FOR EACH LAYOUT BY SIMULATION

| Line          | Characteristic of crosstalk <sup>a</sup> (objective function highlighted) |        |        |       |        |        |

|---------------|---------------------------------------------------------------------------|--------|--------|-------|--------|--------|

| layout        | $P_t$                                                                     | $V_t$  | $A_t$  | $P_r$ | $V_r$  | $A_r$  |

| Spiral        | 14.44                                                                     | 1014.1 | 1064.0 | 28.19 | 100.03 | 364.63 |

| Meander       | 48.91                                                                     | 80.250 | 1369.6 | 32.90 | 1024.5 | 460.51 |

| Dz            | 84.78                                                                     | 238.29 | 577.66 | 22.82 | 929.87 | 247.94 |

| Pattern<br>IV | 126.93                                                                    | 149.72 | 847.94 | 6.04  | 1128.9 | 314.20 |

<sup>a</sup>Unit for Peak is mV, Variance (20 ps)<sup>2</sup>, and Area mV×(20 ps).

direction changes randomly, and it is extended until the line joins the thread of the existing layout. Any disconnected lines from the mutation operation are removed. After the mutation, we again adjust the line length as explained in Section III-B1.

### **IV. OPTIMIZATION RESULTS**

The proposed method has been applied to design a delay line with the following conditions: The cell size is 4 mm, line width is 1.92 mm, both  $C_{\text{width}}$  and  $C_{\text{height}}$  are 8, and z (the size of the population) is 100. The procedure in Section III-B is repeated 500 times. The conditions

Fig. 9. Waveform of "Pattern IV" delay line ( $P_r$  is minimized).

TABLE III

Measurement of Peak Value for Each Layout

| Line layout | $P_t$ | $P_r$ (mV) |

|-------------|-------|------------|

| Spiral      | 14.86 | 37.84      |

| Meander     | 52.70 | 59.46      |

| Dz          | 16.22 | 36.49      |

| Pattern IV  | 9.46  | 32.43      |

for the crosstalk estimation and experimental measurement are listed in Table I. Three kinds of objective functions in (3) from TDT and TDR waveforms are chosen, and the results are explained in the following sections.

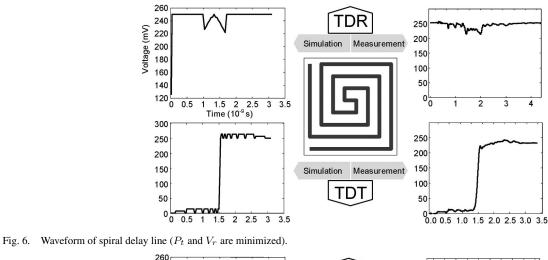

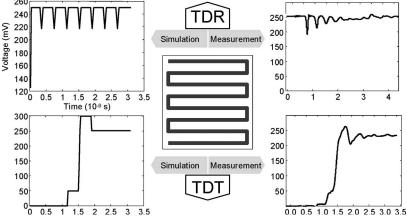

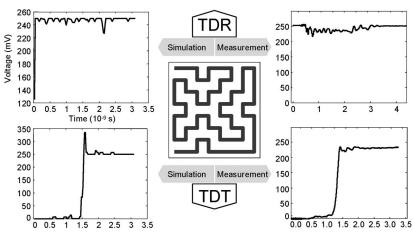

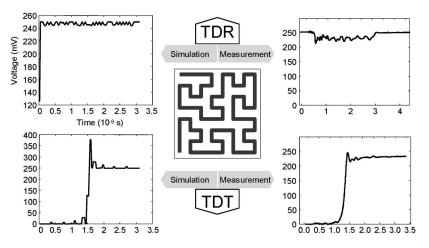

## A. Crosstalk in TDT Waveform

$P_t$ ,  $A_t$ , and  $V_t$  of TDT waveform (the subscript t refers to the characteristic from TDT waveform) are chosen as the objective functions, and three different types of line layouts are obtained. Note that the lower left waveforms in Figs. 6–8 are discussed in this section. In minimizing  $P_t$ , a spiral delay line is obtained (Fig. 6), which is also suggested in [1] and [10]. The TDT waveform of the spiral line (the lower left one in Fig. 6) is interpreted as follows: As the line travels from the starting point and winds to the center, the parallel victim line sections are getting shorter, and this contributes to the shortening of widths of the rectangular type crosstalk as approaching the rising edge. When  $V_t$  is chosen to be minimized, the modified GA yields a meander line (Fig. 7), which is widely used in industries [1], [2], [10], [11]. The two rectangular waves before and after the rising edge in the TDT waveform in Fig. 7 denote an accumulation of the NE crosstalk at the preceding and the following victims, respectively.

In the case of minimizing  $A_t$ , on the other hand, we obtain a new layout not found in the literature; the line is zigzagging in a diagonal direction, as shown in Fig. 8. This new layout is therefore named as the "Dz delay line." The sharp peak in the TDT waveform in Fig. 8 is the result from the "U-turn" sections where the NE crosstalk is generated right after the step pulse (a total of 12 U-turn sections are found).

The simulation results for values of  $P_t$ ,  $V_t$ , and  $A_t$  of the TDT waveform for each line layout are shown from the second to the fourth columns in Table II. For each characteristic, the optimal solution is highlighted, and the corresponding optimal layout is found from the first column. For example, for  $P_t$ , "14.44" is highlighted, and the optimal layout for minimizing  $P_t$  is "Spiral."

## B. Crosstalk in TDR Waveform

The crosstalk at the starting point is calculated, and similar objective functions,  $P_r$ ,  $V_r$ , and  $A_r$ , are considered for the TDR waveform (the subscript r refers to the characteristics from TDR waveform). In this section, the upper left waveforms in Figs. 6, 8, and 9 are discussed. For the layout where  $P_r$  is minimized, it is difficult to describe the line pattern (Fig. 9, named as "pattern IV" tentatively); the scattered U-turn sections contribute to the asynchronous accumulation of the crosstalk on the TDR waveform in Fig. 9. However, for either case where  $V_r$ or  $A_r$  is minimized, we obtain the same result as the case where  $P_t$ or  $A_t$  is minimized, respectively. When  $V_r$  is chosen as the objective function, the same spiral delay line is obtained with the opposite wound direction. The two valleys from TDR waveform in Fig. 6 come from the first half travel to the center and the second half travel to the ending point. We can conclude that  $P_t$  and  $V_r$  can be minimized simultaneously. For the minimization of A, the Dz delay line (Fig. 8) is obtained, showing that minimizing A at either TDT or TDR waveform is the same optimization task. The simulation results for  $P_r$ ,  $V_r$ , and  $A_r$  of TDR waveform for the optimum layouts are shown in the last three columns in Table II.

### V. MANUFACTURE OF CIRCUITS AND EXPERIMENTATION

The four types of line layouts, the meander line, the spiral line, the Dz line, and pattern IV, are manufactured, and the measured waveforms are compared with the simulation results in Section IV. A step function ( $T_r = 70 \text{ ps}$ ;  $V_{\text{in}} = 250 \text{ mV}$ ) is introduced from the starting point, and the TDT/TDR waveform is captured using an oscilloscope. The measured waveforms are shown in the right side of Figs. 6–9.

For the spiral line, the TDT/TDR waveform captured by the oscilloscope, which is shown in Fig. 6, proves that it is an optimal layout for the minimum  $P_t$  and  $V_r$ . The meander line shown in Fig. 7, which is obtained to provide the minimum  $V_t$ , reveals a similar waveform to the simulation. However, the triangular wave in the measured TDR waveform is getting lower and wider because of increasing  $T_r$ , which is not considered in the estimation. The newly found Dz line, corresponding to the minimum  $A_t$  and  $A_r$ , shows agreements between the simulation and the measurement, as shown in Fig. 8, except the sharp rise in the simulated TDT waveform, which is not observed in the measurement because of the low resolution of the oscilloscope. However, in the real measurement, the Dz line shows its excellence in conveying a step function to the ending point with minimum crosstalk, which is the best TDT waveform among the four types of layouts. Pattern IV in Fig. 9 shows similar waves as the Dz line. A higher peak in the TDT waveform than the one from the Dz line is observed, although TDR waveforms are very similar to each other.

The measured peak values are listed in Table III for comparison with the simulations.

### VI. CONCLUSION

The modified version of GA for the design of a delay line is introduced, and the optimal designs are verified by measuring crosstalk with manufactured PCB boards. Because GA requires a large number of function evaluations, a fast and efficient way of crosstalk calculation is proposed by discretizing the line into segments and superposing the crosstalk from each line segment. The methodology of making offsprings and mutation for the discretized line layout chromosome is suggested. The proposed GA has shown the excellence; we obtained the well-known layouts: the spiral and the meander layouts. In addition, a new layout named Dz layout was found for the minimum disturbance area of the unadulterated waveform. The optimum layouts are manufactured, and the measured waveforms were compared with the simulation results.

In calculating crosstalk, we have made simplifying assumptions, although a more elaborate model may be adopted: 1) The crosstalk is generated only at the parallel adjacent line, and 2) the rising time of the step function  $(T_r)$  is consistent until it travels to the ending point. The current version of the modified GA has an exponentially increasing time complexity as the PCB board size  $(C_{width} \text{ and } C_{height})$  increases. To alleviate this problem, a better scheme for the definition of chromosome (currently composed of 3 bits), as well as a fast-converging algorithm, is necessary.

#### REFERENCES

- R. B. Wu and F. L. Chao, "Flat spiral delay line design with minimum crosstalk penalty," *IEEE Trans. Compon. Packag. Technol.*, vol. 19, no. 2, pp. 397–402, May 1996.

- [2] R. B. Wu and F. L. Chao, "Laddering wave in serpentine delay line," *IEEE Trans. Compon. Packag. Technol.*, vol. 18, no. 4, pp. 644–650, Nov. 1995.

- [3] B. J. Rubin and B. Singh, "Study of meander line delay in circuit boards," *IEEE Trans. Microw. Theory Tech.*, vol. 48, no. 9, pp. 1452–1460, Sep. 2000.

- [4] I. Ndip, W. John, and H. Reichl, "Minimizing reflections and cross-talk in chip packages," in *Proc. 7th Electron. Packag. Technol. Conf.*, 2005, pp. 44–48.

- [5] K. S. Jhang, "Layer assignment for crosstalk minimization in a three layers gridded channel routing," in *Proc. 5th Int. Conf. VLSI CAD*, 1997, pp. 403–405.

- [6] S. Y. Kulkarni and K. V. V. Murthy, "Multichip module structures for minimizing crosstalk effects in high-speed applications," in *Proc. Int. Conf. Electromagn. Interference Compat.*, 1995, pp. 34–39.

- [7] M. A. Elgamel and M. A. Bayoumi, "An efficient minimum area spacing algorithm for noise reduction," in *Proc. Electron., Circuits Syst.*, 2003, pp. 862–865.

- [8] T. Y. Ho, Y. W. Chang, S. J. Chen, and D. T. Lee, "Crosstalk- and performance-driven multilevel full-chip routing," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 24, no. 6, pp. 869–878, Jun. 2005.

- [9] J. Lienig, "A parallel genetic algorithm for performance-driven VLSI routing," *IEEE Trans. Evol. Comput.*, vol. 1, no. 1, pp. 29–39, Apr. 1997.

- [10] W. D. Guo, G. H. Shiue, C. M. Lin, and R. B. Wu, "Comparisons between serpentine and flat spiral delay lines on transient reflection/transmission waveforms and eye diagrams," *IEEE Trans. Microw. Theory Tech.*, vol. 54, no. 4, pp. 1379–1387, Jun. 2006.

- [11] O. M. Ramahi, "Analysis of conventional and novel delay lines: A numerical study," *Appl. Comput. Electromagn. Soc. J.*, vol. 18, no. 3, pp. 181– 190, Nov. 2003.

- [12] K. C. Gupta, R. Garg, I. Bahl, and P. Bhartia, *Microstrip Lines and Slotlines*, 2nd ed. Hoboken, NJ: Wiley, 2000, ch. 3.

- [13] S. H. Hall, G. W. Hall, and J. A. McCall, *High-Speed Digital System Design*. Norwood, MA: Artech House, 1996, ch. 8.

- [14] A. Feller, H. R. Haupp, and J. J. Digiacomo, "Crosstalk and reflections in high-speed digital systems," in *Proc. AFIPS Fall Jt. Comput. Conf.*, 1965, vol. 27, pp. 511–525.

- [15] G. Kim, D. G. Kam, and J. Kim, "TDR/TDT analysis by crosstalk in single and differential meander delay lines for high speed PCB applications," in *Proc. Conf. Rec. IEEE Int. Symp. Electromagn. Compat.*, vol. 3, pp. 657–662.

- [16] Z. Michalewicz, Genetic Algorithms Plus Data Structures Equals Evolution Programs. New York: Springer-Verlag, 1996, ch. 1, 3. 3rd rev.

# On Complete Functional Broadside Tests for Transition Faults

Hangkyu Lee, Irith Pomeranz, and Sudhakar M. Reddy

Abstract—It was shown before that tests applied under nonfunctional operation conditions, which are made possible by scanning in an unreachable state, may lead to unnecessary yield loss. To address this issue, functional broadside tests were defined as broadside tests that use only reachable states of the circuit as scan-in states. Earlier procedures for generating functional broadside tests were not complete, i.e., they did not always detect all the detectable faults or prove that all the undetectable faults are undetectable. In this paper, we address the completeness of the functional broadside tests for transition faults. We describe the implementation of a test-generation procedure that can, for every transition fault, either find a functional broadside tests. We present experimental results where complete results are achieved for almost all the benchmark circuits considered.

*Index Terms*—Functional broadside tests, overtesting, reachable state, scan, test generation.

### I. INTRODUCTION

The rapid increase in clock frequency of integrated circuits necessitates the detection of defects that affect the timing behavior of the circuit. Timing defects are typically modeled by delay faults. Transition faults are widely used as a delay-fault model. Test application methodologies for the delay faults in scan designs can be categorized into enhanced scan testing [1], skewed-load testing [2], and broadside testing [3]. All the techniques may suffer from unnecessary yield loss due to overtesting. Even broadside tests, which apply the second vector of every test in functional mode, may result in overtesting [4]. Overtesting for delay faults can be viewed in two ways. Under the first view, overtesting is due to the fact that redundant faults in the original circuit before scan insertion become detectable after scan insertion. It has been observed in [4] that detecting the redundant faults may lead to unnecessary yield loss, i.e., good chips may be discarded as faulty or placed in a lower performance bin due to the detection of a redundant fault. Under the second view, overtesting is caused by

Manuscript received May 3, 2007; revised July 21, 2007. This paper was recommended by Associate Editor N. K. Jha.

H. Lee is with Intel Corporation, Austin, TX 78746 USA (e-mail: hangkyu.lee@intel.com).

I. Pomeranz is with the School of Electrical and Computer Engineering, Purdue University, West Lafayette, IN 47907 USA.

S. M. Reddy is with the Department of Electrical and Computer Engineering, University of Iowa, Iowa City, IA 52242 USA.

Digital Object Identifier 10.1109/TCAD.2008.915531